Three Continents, One Stack

As a kid I'd lose hours to Legos, wiring projects, anything I could take apart and put back together differently. What I was really chasing was that moment when something you built actually comes to life, my own little Frankenstein. That instinct never left.

I'm Ozan, born in Istanbul, raised in Barcelona, now at Boston University studying Computer Engineering. I chose CE specifically because it scared me a little, and that's always been my signal to go. It's also the one field where you can trace a complete path from electrons to a web app, and then hand that web app to someone on the other side of the world. Speaking five languages gave me a specific ambition: I don't just want to build things, I want to spread them. The engineers who actually change the world are the ones who can communicate across every boundary.

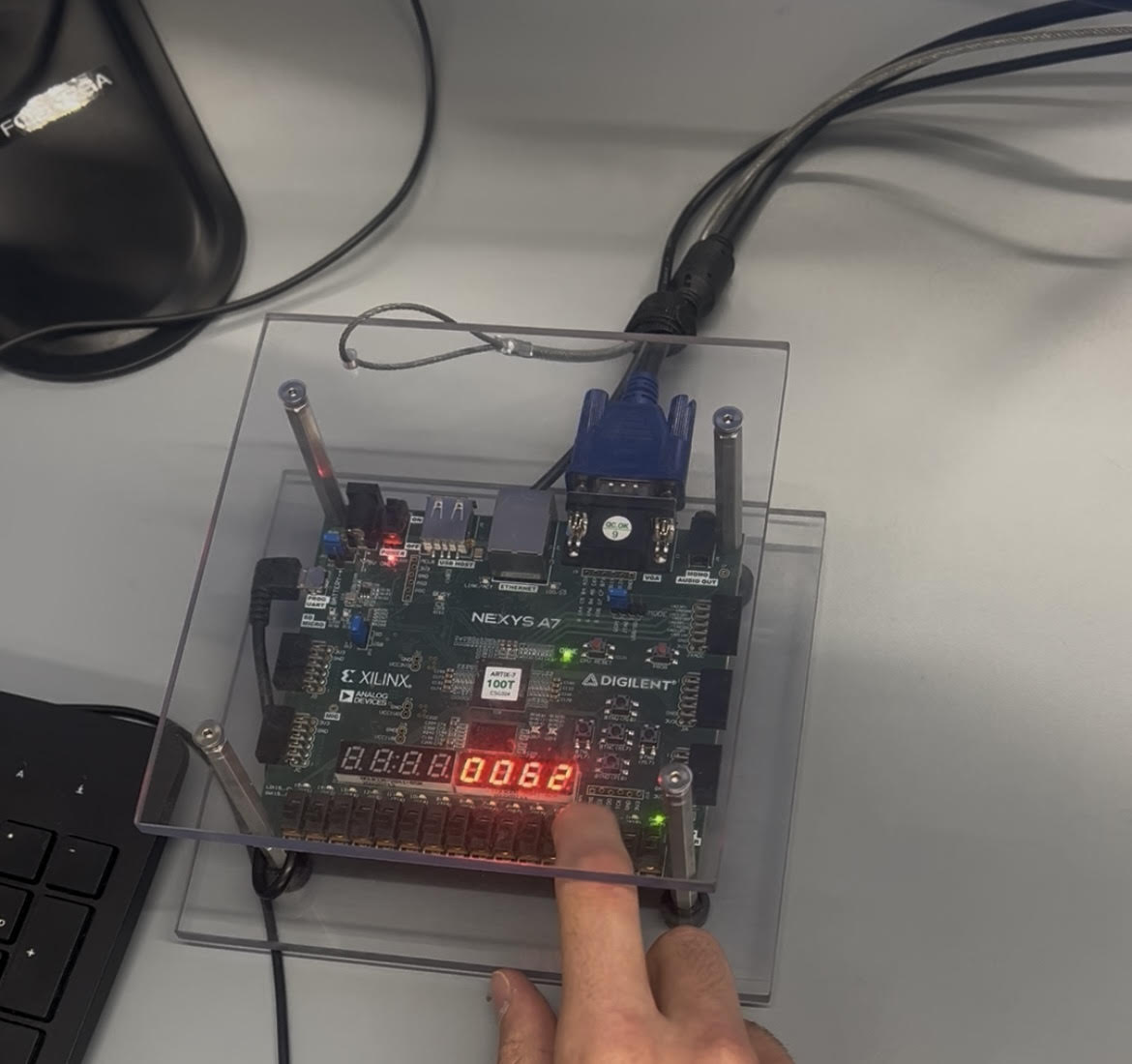

My strongest skill is probably obsessive curiosity. The Color Sorter won a class award not because of fancy parts, but because I ran hundreds of calibration trials, obsessed over why the sensor drifted in different lighting, and engineered the thresholds until it hit 95% consistently.

Outside the lab I lead. As a BU Engineering Student Advisor I mentor incoming freshmen, and as a youth basketball coach I run drills, manage game-day decisions, and teach kids to compete as a unit. I'm also active in the AI Society, Mars Rover Club, and Barbell Club. Piano, surfing, and an embarrassing record collection keep me human.

'27